네패스, AI 반도체 시대 위한 '세계 최초' 8 레이어 RDL 인터포저 기술 공개

기판 없이 패키징 가능 "전체 칩 사이즈 줄여줘…반도체 패키지 경쟁력 확보"

박기훈 기자

| pkh@newsprime.co.kr |

2024.06.03 15:17:15

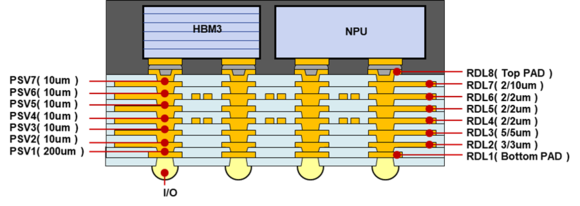

8 레이어 RDL 인터포저 구조도. ⓒ 네패스

[프라임경제] 네패스(033640)가 현지시간으로 지난달 28일부터 31일까지 미국 콜로라도주 덴버에서 열린 제74회 전자부품기술학회(ECTC)에서 팬아웃 기반 RDL 인터포저 기술을 선보였다고 3일 밝혔다.

네패스는 행사 이튿날인 29일 '미래 패키지 재료 기술의 열기계적 응력 및 신뢰성 분석(Thermo-mechanical Stress and Reliability Analysis for Materials in Future Packaging)' 세션에서 '팬아웃 RDL 인터포저와 실리콘 브릿지 기술을 기반으로 한 싱글 및 멀티 NPU 칩렛 이종 접합 패키징(Single and Multi NPU Chiplet Heterogeneous Integration Packaging Based on Fan-Out RDL Interposer With Silicon Bridge Technology)' 주제의 논문과 함께 첨단 패키징 기술 현황을 공유했다.

해당 기술은 인터포저 위에 여러 칩을 수직.수평으로 연결하는 칩렛 패키징을 실리콘(Si) 인터포저 대신 팬아웃 공정 기반의 재배선(RDL) 인터포저로 구현한 것이 특징이다.

인공지능(AI) 반도체 수요 증가에 따라 칩렛 패키징 기술이 주요 화두인 가운데 우수한 전기적 특성 및 생산 효율성, 제조 비용 절감 등의 장점으로 현장 참가자들의 높은 관심을 받았다는 것이 회사 측의 설명이다.

특히 이번 ECTC에서는 세계적으로 6 레이어 RDL 인터포저 기술이 일반적인 상황에서 기존보다 2 레이어를 더 쌓은 8 레이어 RDL 인터포저 기술을 개발 및 공유했다. 이는 기존에 기판(Substrate)이 필요한 구조에서 기판이 필요 없는(Substrate-less) 구조가 되었다는 점에서 의미가 있다.

즉, 기존의 경우 RDL 인터포저 제작 및 칩 접착과 몰딩 등의 공정 이후에 기판(Substrate) 위에 추가적으로 플립칩 공정을 진행해야 한다.

하지만 8 레이어 공정은 기판 위에 플립칩 공정이 필요 없어지면서 별도 기판없이 패키징이 가능해 전체 패키지 사이즈를 줄일 수 있음은 물론, 공정이 간소화되면서 공정 효율성이 높아지고 복잡했던 기판과의 전기적 연결이 간결해지면서 우수한 전기적 특성 구현이 가능하게 해준다.

네패스 관계자는 "RDL 인터포저는 다양한 칩들을 연결하는데 적합한 솔루션으로 앞으로 시장 성장 잠재력이 매우 큰 추론용 인공지능의 엣지 컴퓨팅 분야 등에서 폭넓게 활용될 것으로 예상된다"고 말했다.

이어 "향후 네트워크 강화 및 고객사 기술 협력을 통해 상용화에 적극 나서 글로벌 반도체 패키지 경쟁력을 확보해 나갈 계획"이라고 전했다.

ⓒ 프라임경제(http://www.newsprime.co.kr) 무단전재 및 재배포금지

![[포토] 'AI 공존' TCK '2026 인사이트 포럼'](https://www.newsprime.co.kr//data/cache/public/photos/cdn/20260311/art_726964_1773380545_245x140.jpg)